# A First Performance Analysis of the Admission Control in the HaRTES Ethernet Switch

Inés Álvarez, Mladen Knezic, Luís Almeida, Julián Proenza

## Flexible Time-Triggered

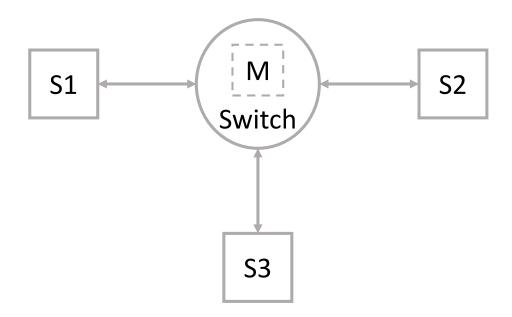

- Time-triggered and event-triggered traffic.

- Master/multi-slave architecture.

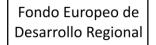

- Communication divided in Elementary Cycles.

## Flexible Time-Triggered

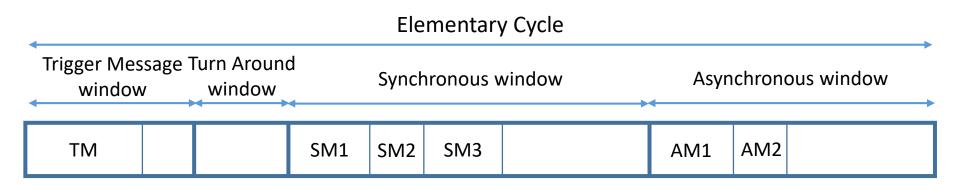

- HaRTES architecture: master inside the switch.

- Communication done through streams.

- Slaves can request changes in streams → Admission

Control.

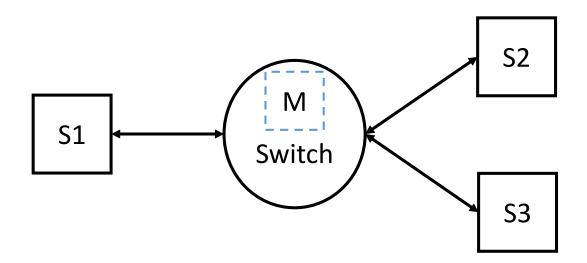

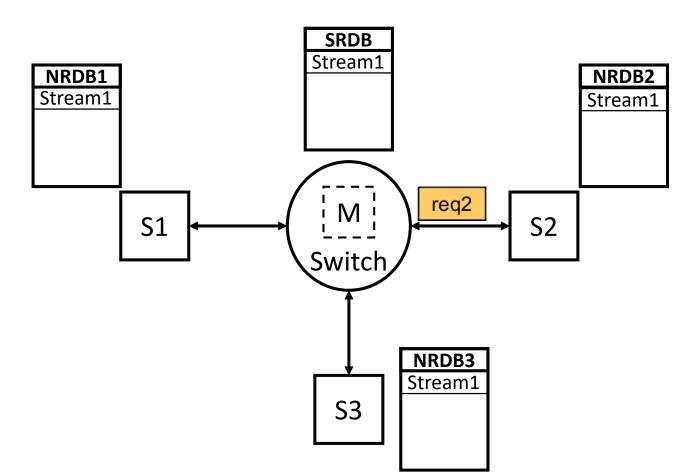

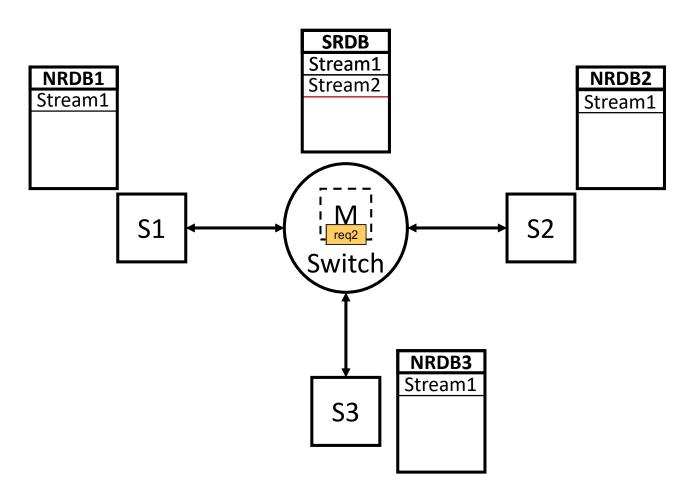

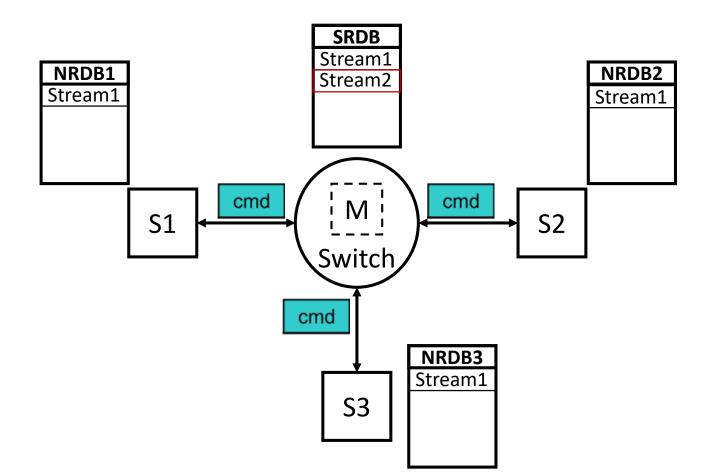

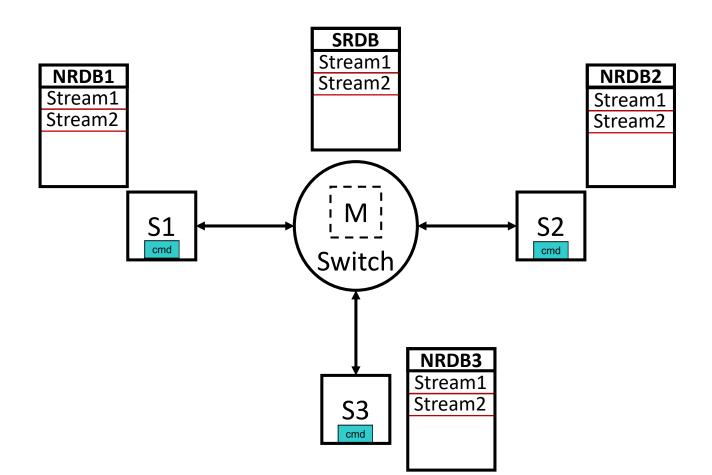

## Stream information in **SRDB** and **NRDB**s

Slave sends **request** to the Master

Master **processes** the request

### Stream information in NRDBs and SRDB

### Stream information in NRDBs and SRDB

## Admission Control Study

## Study the performance of the Admission Control process

## OMNeT++ Model

Knezic, M., Ballesteros, A. and Proenza, J., "Towards extending the OMNeT++ INET framework for simulating fault injection in Ethernetbased Flexible Time-Triggered systems," in Proceedings of the 2014 IEEE Emerging Technology and Factory Automation (ETFA), Sept 2014.

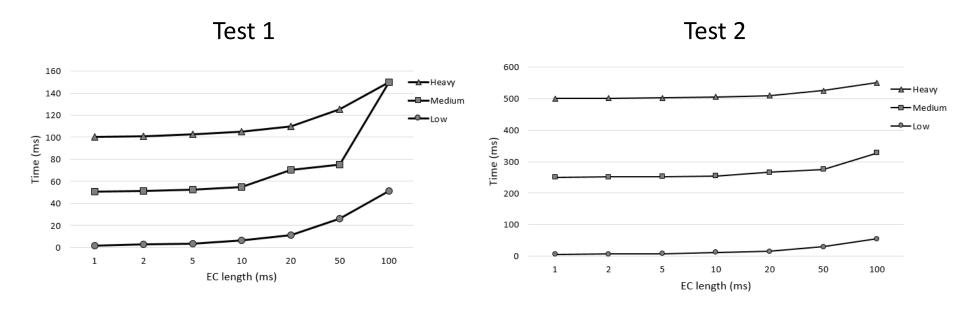

## Experiments and Results

|        | Network Load (ms) |        |       | Concurrency |

|--------|-------------------|--------|-------|-------------|

|        | Low               | Medium | Heavy | (# nodes)   |

| Test 1 | 1                 | 50     | 100   | 1           |

| Test 2 | 1                 | 50     | 100   | 10          |

## **Questions?** Please meet me at the poster!

#### A First Performance Analysis of the Admission Control in the HaRTES Ethernet Switch

Inés Álvarez<sup>1</sup>, Mladen Knezic<sup>2</sup>, Luís Almeida<sup>1</sup>, Julián Proenza<sup>5</sup> Instituto de Telecomunicações, Universidade do Porto, Portugal,

ines.alvarez.91@gmail.com, ida@fe.up.pt Faculty of Electrical Engineering, University of Banja Luka, Bosnia and Herzegovina,

Mladen.knezic@etfbl.net Departament de Matemàtiques i Informàtica, Universitat de les files Balears, Spain, Julian.proenza@ulb.es

Fondo Europeo de Desarrollo Regional

#### Abstract

There is a proving interest in developing embedded options capable of being deployed in dynamic environments that may impredictable manners. When such options are Distributed Embedded Systems (DESS) they must adult friendability and indeed of their authority, schaling their environ. On the network. On the other hand, there is a done travel in Indeed to you would using Debender-based protocols with network of DESs.

Nevertheless, Ethernet lacks appropriate support for real-time (RT) communications, mixing different RT traffic and on-line management of the Quality of Service (QoS), Several implementations of the Fieuble Time-Tiggered (FTT) protocol over Ethernet were proposed to cope with these drawbacks.

FTT is a master/multi-clave protocol that is able to simultaneously convey real and non-real-time traffic and provides mechanisms for dynamically changing the Opti of the network, including Admission Control (AC). The AC is a fundamental component for on-line network management, since it guarantees that each participant gets the required QoS.

This paper presents the implementation in OMMeT++ of a simulation model of the AC in the FTT HaRTIS switch as well as a preliminary performance study using that model.

#### Flexible Time-Triggered

Flexible Time-Triggered supports event and time-triggered traffic in a flexible manner. Follows a master/multi-slave architecture. The master organises the communication in dots of fixed duration called Elementary Cycles, by sending the so called Trigger Message to synchronise and trigger the communication among dayes.

The communication is carried out through virtual communication channels called message streams. First daves ask for the creation of the stream and afterwards ask to attach as publisher or subscribers.

The selected architecture is HaRTES, that contains the master node embedded inside the Switch.

#### Admission Control in HaRTES

Stream information is saved in the SRDB The master broadcast the result to the in master and the NRDBs in nodes to the master with the GoS information updates the SRDB.

#### Modelling HaRTES' Admission Control and Quantitative Performance Analysis

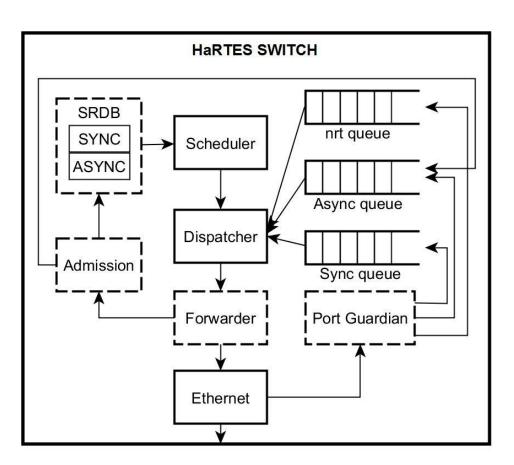

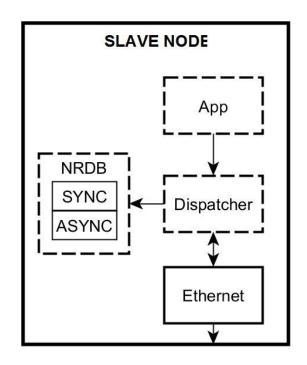

#### OMNeT++ Model

Model of the HaRTES switch and a Slave node in OMNeT++. Dashed lines indicate modules affected by the Admission Control implementation

- . Duration of the EC has a sever impact on the duration of the Admission Control

- Level of concurrency impacts the duration of the Admission Control.

- Difficult for slaves to predict the duration of the Admission Control

#### Experiments

Study the performance of the Amission Control. Specifically, study the Impact of the EC length and the level of concurrency

Test the performance under different load conditions, since the load of the network affects to the duration of the analysis carried out by the master

Network with a single switch and ten slave nodes. The table shows the parameters used in every test.

(f nodes) Test 1 100

#### Conclusions and Future Work

- Study the Impact of the BC length and level of concurrency on the performance of the Admission

- One-hop network with a single switch and ten slave nodes

- Difficult for dayes to determine the duration of the AC -> Needed a confirmation for relected requests to prevent further performance and reliability degradation.

- Extend the model to compare with the Admission Control of the FTT-SE architecture

- Extend the comparison to include the Stream Reservation Protocol implemented in Audio Video

[Kinsalc et al. 2014] M. Kineck, A. Ballesterox, and J. Proezza, "Towards extending the OMNeT++ INET framework for simulating fault injection is Ethernethased Fiesible Time Triggered systems," in Proceedings of the 2014 IEEE Emerging Technology and Factory Automation (ETFA), Sept 2014.